在數字集成電路設計流程中,軟件開發環境是Verilog HDL設計與綜合不可或缺的核心環節。本部分將重點探討軟件開發工具及其在現代IC設計中的關鍵作用。

一、軟件開發環境概述

數字IC設計依賴于一系列專業軟件工具,包括代碼編輯器、仿真器、綜合工具和時序分析器等。這些工具共同構成一個完整的開發環境,支持從設計輸入到物理實現的全流程。常見的環境如Cadence、Synopsys和Mentor Graphics提供的EDA(電子設計自動化)套件,它們為Verilog HDL提供了強大的開發平臺。

二、Verilog HDL設計與仿真工具

設計階段,工程師使用文本編輯器或集成開發環境(IDE)編寫Verilog代碼。工具如Vim、Emacs或專用IDE(如Vivado、Quartus Prime)提供語法高亮、自動補全和錯誤檢查功能,提升編碼效率。仿真工具如ModelSim、VCS則用于驗證設計邏輯的正確性,通過模擬輸入信號并觀察輸出響應,確保功能符合規格。

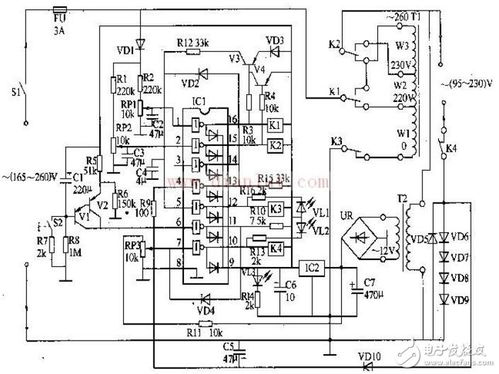

三、綜合與優化工具

綜合是將Verilog HDL描述轉換為門級網表的過程,工具如Design Compiler(Synopsys)或RTL Compiler(Cadence)執行此任務。這些軟件分析代碼,優化邏輯結構,并映射到目標工藝庫,同時考慮面積、功耗和時序約束。綜合后,需進行靜態時序分析(STA)以確保設計滿足時序要求。

四、軟件開發中的最佳實踐

有效的軟件開發需要遵循模塊化設計、可重用代碼和版本控制(如Git)等原則。自動化腳本(如Tcl或Python)可用于管理設計流程,減少人為錯誤。持續集成和測試框架可加速驗證周期,提高設計可靠性。

五、未來趨勢與挑戰

隨著人工智能和云計算的興起,EDA工具正融入機器學習算法以優化綜合和驗證。開源工具如Yosys和Verilator也在崛起,降低了設計門檻。軟件開發面臨復雜設計規模增大和功耗優化的挑戰,要求工程師不斷更新技能。

軟件開發是Verilog HDL設計與綜合的基石,通過高效工具和規范流程,推動數字集成電路的創新與實現。掌握這些工具不僅能加速設計周期,還能確保芯片的高質量與可靠性。