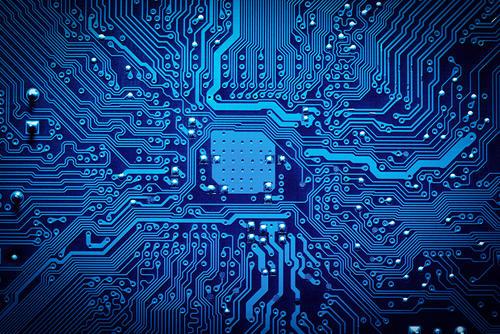

模擬集成電路(Analog Integrated Circuit,簡稱模擬IC)在現代電子系統中扮演著至關重要的角色,廣泛應用于通信、醫療、汽車和消費電子等領域。與數字集成電路不同,模擬IC處理連續信號,其設計過程更加復雜,需要考慮噪聲、功耗、線性度和穩定性等關鍵參數。本文將介紹模擬集成電路設計的基本流程和仿真方法,幫助初學者和工程師理解這一領域的核心要點。

模擬集成電路設計通常從系統規格定義開始。設計者需要明確電路的功能需求,如增益、帶寬、電源電壓和負載條件等。這一步至關重要,因為它直接影響后續的電路拓撲選擇和器件尺寸確定。例如,在運算放大器設計中,需確定開環增益、相位裕度和輸出擺幅等參數。

接下來是電路拓撲選擇階段。根據規格要求,設計者選擇合適的電路結構,如差分對、電流鏡或反饋網絡。常見拓撲包括共源共柵放大器、折疊級聯運放等,每種結構都有其優缺點。例如,共源共柵結構能提高輸出阻抗和增益,但可能增加功耗和面積。

器件尺寸確定是設計過程中的核心環節。設計者需使用模擬仿真工具(如SPICE)來優化晶體管尺寸、偏置電流和電阻值等。這一步驟依賴于工藝模型文件,這些文件描述了特定半導體工藝(如CMOS或BiCMOS)中器件的電氣特性。通過迭代仿真,設計者調整參數以滿足性能指標,同時考慮工藝變異和溫度影響。

仿真在模擬IC設計中不可或缺。它分為直流分析、交流分析、瞬態分析和噪聲分析等類型。直流分析用于檢查偏置點穩定性;交流分析評估頻率響應和穩定性;瞬態分析觀察時域行為;噪聲分析則幫助優化信噪比。例如,在射頻電路中,仿真可以預測諧波失真和互調失真。

設計完成后,還需進行版圖設計,將電路圖轉換為物理布局。版圖設計需遵循設計規則,確保可制造性,并考慮寄生效應(如電容和電阻)對性能的影響。之后,通過后仿真驗證版圖的電氣特性,確保與原理圖仿真一致。

模擬集成電路設計與仿真是多學科融合的過程,涉及電路理論、半導體物理和計算機輔助設計工具。隨著工藝節點不斷縮小,設計挑戰日益增加,但通過系統化方法和先進仿真技術,工程師能夠開發出高性能、低功耗的模擬IC,推動電子技術的進步。